2022-07-19 0

封装

经过之前几个工艺处理的晶圆上会形成大小相等的方形芯片(又称“单个晶片”)。下面要做的就是通过切割获得单独的芯片。刚切割下来的芯片很脆弱且不能交换电信号,需要单独进行处理。这一处理过程就是封装,包括在半导体芯片外部形成保护壳和让它们能够与外部交换电信号。整个封装制程分为五步,即晶圆锯切、单个晶片附着、互连、成型和封装测试。

1、晶圆锯切

要想从晶圆上切出无数致密排列的芯片,我们首先要仔细“研磨”晶圆的背面直至其厚度能够满足封装工艺的需要。研磨后,我们就可以沿着晶圆上的划片线进行切割,直至将半导体芯片分离出来。

晶圆切割划片机技术有三种:刀片切割、激光切割和等离子切割。

刀片切割是指用金刚石刀片切割晶圆,这种方法容易产生摩擦热和碎屑并因此损坏晶圆。

激光切割的精度更高,能轻松处理厚度较薄或划片线间距很小的晶圆。

等离子切割采用等离子刻蚀的原理,因此即使划片线间距非常小,这种技术同样能适用。

2、单个晶片附着

所有芯片都从晶圆上分离后,我们需要将单独的芯片(单个晶片)附着到基底(引线框架)上。基底的作用是保护半导体芯片并让它们能与外部电路进行电信号交换。附着芯片时可以使用液体或固体带状粘合剂。

3、互连

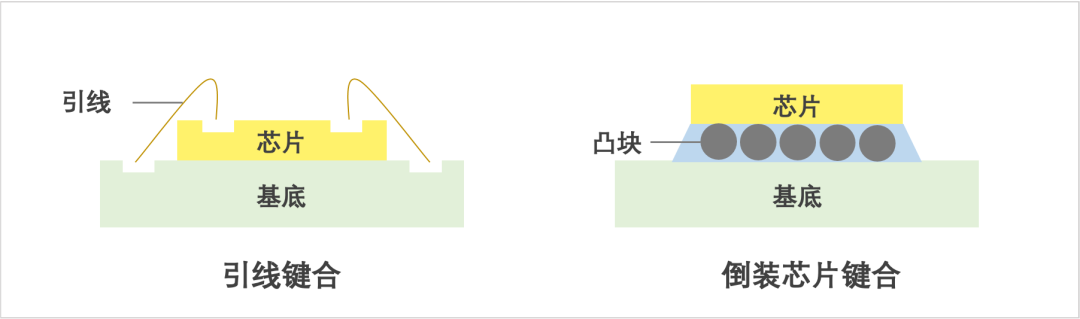

在将芯片附着到基底上之后,我们还需要连接二者的接触点才能实现电信号交换。这一步可以使用的连接方法有两种:使用细金属线的引线键合和使用球形金块或锡块的倒装芯片键合。引线键合属于传统方法,倒装芯片键合技术可以加快半导体制造的速度。

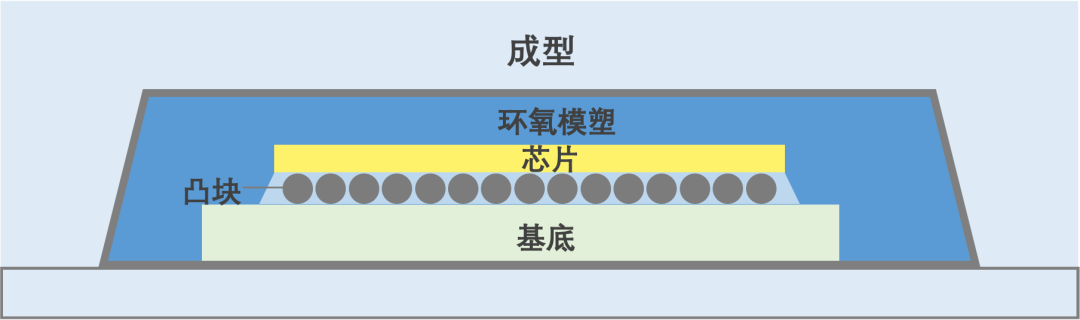

4、成型

完成半导体芯片的连接后,需要利用成型工艺给芯片外部加一个包装,以保护半导体集成电路不受温度和湿度等外部条件影响。根据需要制成封装模具后,我们要将半导体芯片和环氧模塑料 (EMC) 都放入模具中并进行密封。密封之后的芯片就是最终形态了。

5、封装测试

已经具有最终形态的芯片还要通过最后的缺陷测试。进入最终测试的全部是成品的半导体芯片。它们将被放入测试设备,设定不同的条件例如电压、温度和湿度等进行电气、功能和速度测试。这些测试的结果可以用来发现缺陷、提高产品质量和生产效率。

随着芯片体积的减少和性能要求的提升,封装在过去数年间已经历了多次技术革新。面向未来的一些封装技术和方案包括将沉积用于传统后道工艺,例如晶圆级封装(WLP)、凸块工艺和重布线层 (RDL) 技术,以及用于前道晶圆制造的的刻蚀和清洁技术。

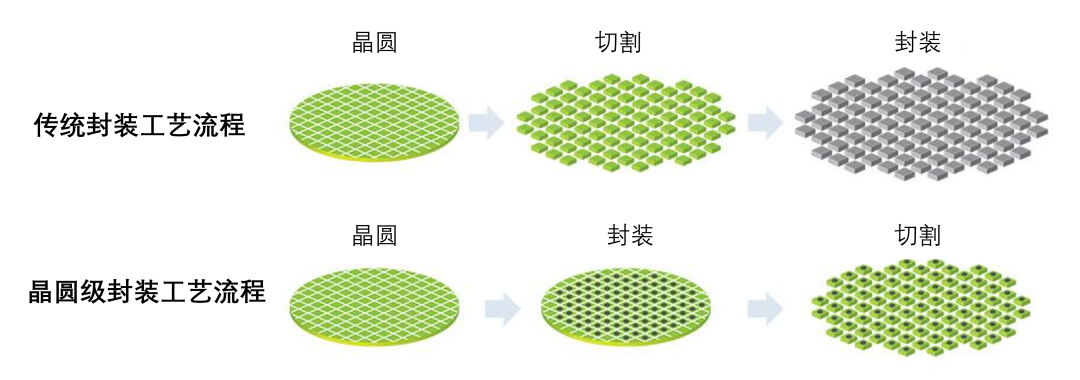

1)晶圆级封装

传统封装需要将每个芯片都从晶圆中切割出来并放入模具中。晶圆级封装(WLP)则是先进封装技术的一种, 是指直接封装仍在晶圆上的芯片。WLP的流程是先封装测试,然后一次性将所有已成型的芯片从晶圆上分离出来。与传统封装相比,WLP的优势在于更低的生产成本。

2)先进封装

先进封装可划分为2D封装、2.5D封装和3D封装。

更小的2D封装

如前所述,封装工艺的主要用途包括将半导体芯片的信号发送到外部,而在晶圆上形成的凸块就是发送输入/输出信号的接触点。这些凸块分为扇入型(fan-in) 和扇出型 (fan-out) 两种,前者的扇形在芯片内部,后者的扇形则要超出芯片范围。我们将输入/输出信号称为I/O(输入/输出),输入/输出数量称为I/O计数。I/O计数是确定封装方法的重要依据。如果I/O计数低就采用扇入封装工艺。由于封装后芯片尺寸变化不大,因此这种过程又被称为芯片级封装 (CSP) 或晶圆级芯片尺寸封装 (WLCSP)。如果I/O计数较高,则通常要采用扇出型封装工艺,且除凸块外还需要重布线层 (RDL) 才能实现信号发送。这就是“扇出型晶圆级封装 (FOWLP)”。

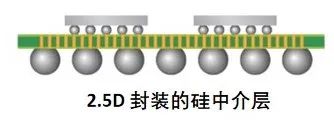

2.5D 封装

2.5D封装技术可以将两种或更多类型的芯片放入单个封装,同时让信号横向传送,这样可以提升封装的尺寸和性能。最广泛使用的2.5D封装方法是通过硅中介层将内存和逻辑芯片放入单个封装。2.5D封装需要硅通孔 (TSV)、微型凸块和小间距RDL等核心技术。

3D 封装

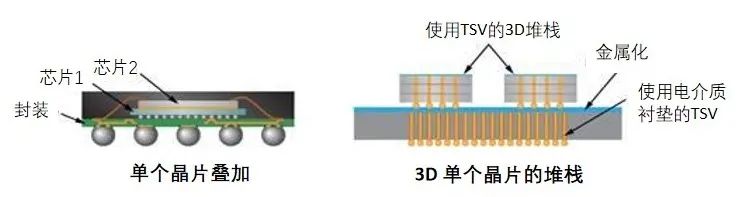

3D封装技术可以将两种或更多类型的芯片放入单个封装,同时让信号纵向传送。这种技术适用于更小和I/O计数更高的半导体芯片。TSV可用于I/O计数高的芯片,引线键合可用于I/O计数低的芯片,并最终形成芯片垂直排列的信号系统。3D封装需要的核心技术包括TSV和微型凸块技术。

138-2371-2890